# An 11 W Ku-band Heterostructure FET with WSi/Au T-shaped Gate

J. Udomoto, S. Chaki, M. Komaru, T. Kunii, Y. Kohno, S. Goto,

K. Gotoh, A. Inoue, N. Tanino, T. Takagi, and O. Ishihara

Optoelectronic and Microwave Devices Laboratory

Mitsubishi Electric Corporation

4-1, Mizuhara, Itami, Hyogo 664, Japan

## ABSTRACT

We developed a Heterostructure FET (HFET) with a high output power and a high power-added efficiency (PAE) at Ku-band. 8 W and 11.2 W output powers were obtained with power-added efficiencies of 48% and 41% and linear gains of 9 dB and 8.6 dB at 12 GHz, respectively. This is the highest power and efficiency ever reported which is achieved by a single FET chip at this frequency.

## I. INTRODUCTION

Demands for high power amplifiers are increasing in microwave communication applications. Much work has been done to improve RF performances, especially output power and power-added efficiency of HFETs, HEMTs, and HBTs at X to Ku-band[1-3]. Both HEMTs and HBTs have high gain and high power density. However, there is not enough data concerning reliability, especially for several watts power class transistors. From the viewpoint of reliability, refractory metal gates are suitable for high power applications because of their

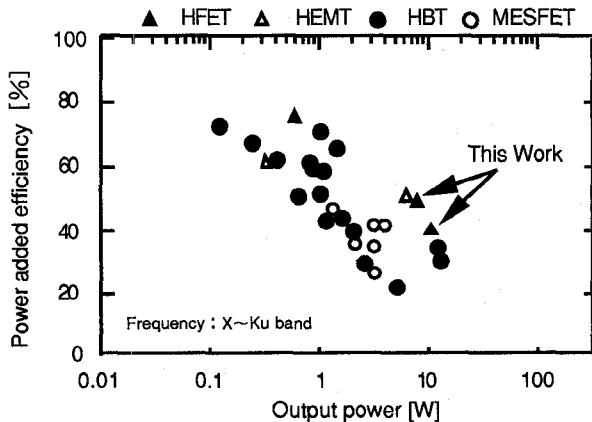

Fig.1 Power performance of a transistor at X-Ku band.

thermal stability[4]. We are developing a GaAs power FET with a sub-half micron WSi/Au T-shaped gate that has higher reliability than Al gate MESFETs[5].

In this paper, we describe an HFET with a sub-half micron WSi/Au T-shaped gate. As shown in Fig.1, it delivers the highest output power and power-added efficiency among single FETs at 12 GHz.

## II. DEVICE DESCRIPTION

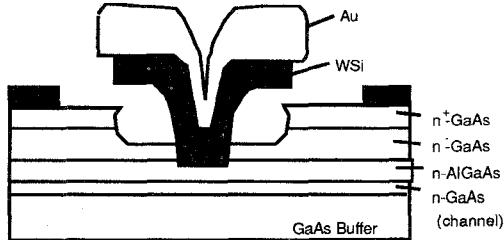

A schematic cross-section of a developed HFET

Fig.2 Schematic cross-section of an HFET with a buried gate.

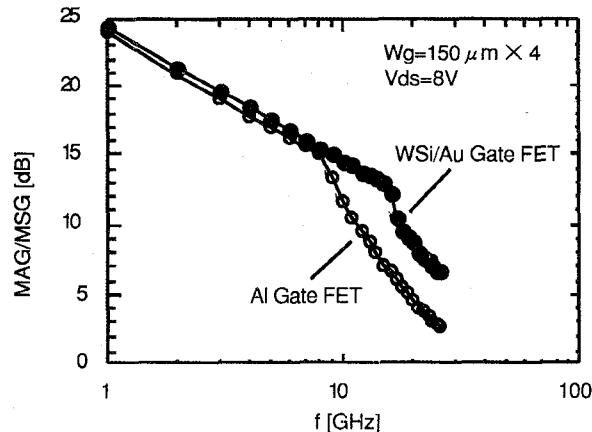

Fig.3 MAG/MSG as a function of frequency.

with a buried gate is shown in Fig.2. The HFET includes a high doped GaAs layer sandwiched between a superlattice buffer layer on the bottom and a low doped AlGaAs layer. We formed the WSi/Au T-shaped gate by using  $\text{SiO}_2$  sidewalls[5]. The gate length is typically  $0.4 \mu\text{m}$ . The WSi of the WSi/Au is employed as a schottky metal for high reliability and the Au is for reducing gate resistance. In order to reduce the influence of surface depletion, a buried gate structure was employed.

Figure 3 shows Maximum Available Gain and Maximum Stable Gain (MAG/MSG) of a WSi/Au gate FET and a conventional Al gate FET as a function of frequency. Because of the reduction of gate resistance, MAG of the WSi/Au gate FET is as high as  $13.9 \text{ dB}$  at  $12 \text{ GHz}$ , which is  $4.3 \text{ dB}$  higher than that of the Al gate

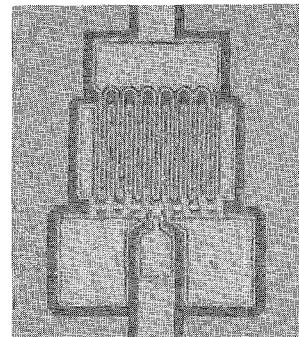

Fig.4 A 2.1mm gate periphery device.

Fig.5 A 23.1mm gate periphery device.

FET.

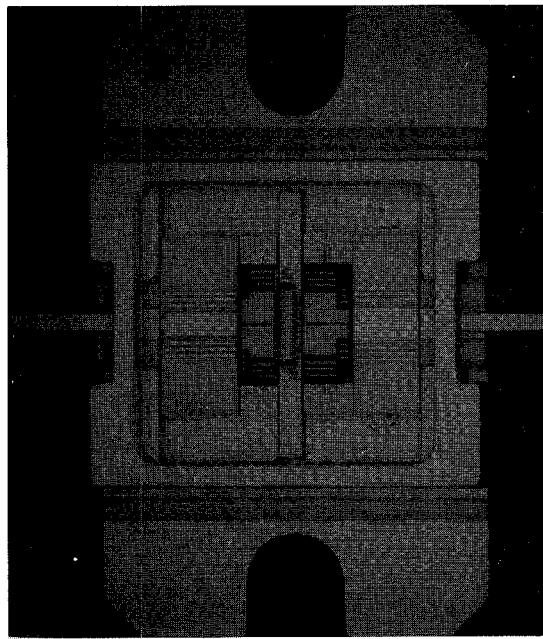

The unit FET that was used for power application at Ku-band is the 2.1 mm gate periphery device shown in Fig.4. The unit gate width  $W_{\text{gu}}$  is  $150 \mu\text{m}$ . To reduce the thermal resistance, the thickness of a GaAs substrate was thinned down to  $30 \mu\text{m}$  and an Au plated heat sink (PHS) structure was adopted. The device that was used for power application is the 23.1 mm gate periphery ( 2.1 mm FET  $\times$  11 ) device shown in Fig.5. The chip size is  $0.58 \times 2.75 \text{ mm}^2$ .

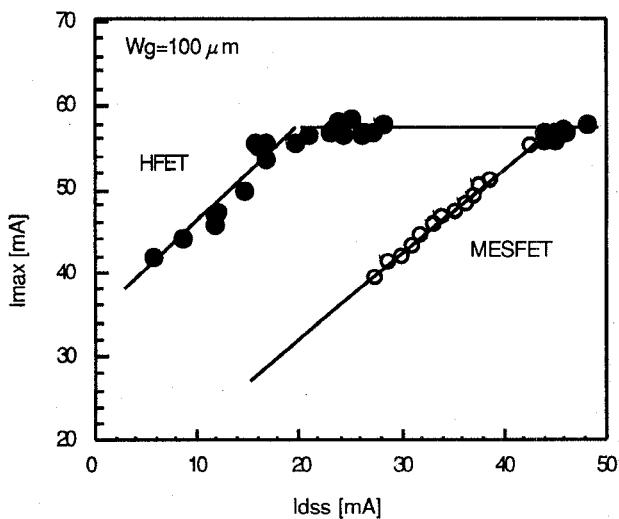

In order to derive high output power, maximum drain current ( $I_{\text{max}}$ ) should be large. Figure 6 shows the  $I_{\text{max}}$  of an HFET and a MESFET as a function of saturation current ( $I_{\text{dss}}$ ). Since the  $I_{\text{max}}$  of an HFET is larger than that of a MESFET, an HFET is expected to have a higher output power density. As shown in Fig.6, the  $I_{\text{max}}$  of an HFET saturates when the  $I_{\text{dss}}$  is more than  $200 \text{ mA/mm}$ . So the most suitable value of the  $I_{\text{dss}}$  is

Fig.6 Imax versus Idss of an HFET and a MESFET.

200 mA/mm. We decided on Idss 200~300 mA/mm to avoid fluctuation.

### III. CIRCUIT DESIGN

It is very difficult to measure the S-parameters of the 23.1 mm gate periphery FET precisely by the on-wafer probing technique, because the input and output impedance becomes too low. So we measured S-parameters of the 2.1 mm gate periphery FET, then calculated the S-parameters of the 23.1 mm gate periphery FET for matching circuit design. A Ku-band power module is shown in Fig.7. The module size is 21.0 × 12.9 mm<sup>2</sup>. The input and output matching circuits consist of a 0.38 mm thick alumina microstrip circuit and a 0.1 mm thick high dielectric constant Barium Titanate ( $\text{BaTiO}_3$ ,  $\epsilon_r = 38$ ) microstrip circuit. For uniform operation of all unit FETs, it is necessary to make each wire length equal. Thus, the line width on the high dielectric substrate should be wider than the distance between gate pads. However, an undesirable propagation mode appears and reduces the output power when the

Fig.7 Ku-band power module.

Fig.8 Measured power-added efficiency and output power as a function of input power.

width of the microstrip line becomes larger than half of the wave length. Therefore, a slit was formed in the microstrip line of the high dielectric substrate. Gate and drain bias circuits are provided on both sides of the module using bias T network.

### IV. PERFORMANCE

The gate-drain breakdown voltage ( $V_{gdo}$ ) was typically  $12\sim14$  V at a reverse current of  $100 \mu\text{A}/\text{mm}$ . The  $Id_{ss}$  of an HFET was typically  $250\sim300 \text{ mA}/\text{mm}$ . The transconductance was typically  $200\sim250 \text{ mS}/\text{mm}$ .

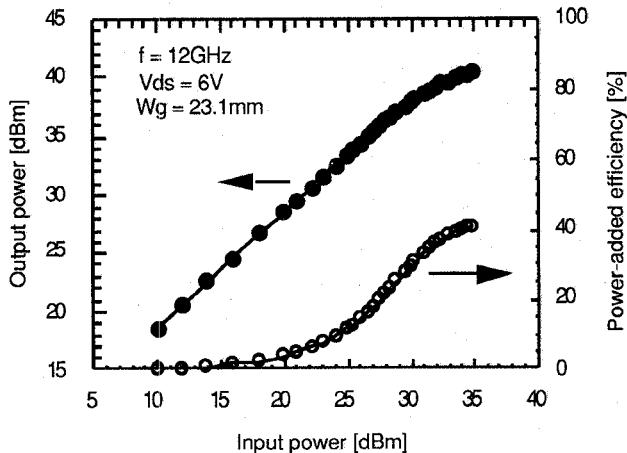

The power characteristics of the 23.1 mm HFET were measured at 12 GHz. Figure 8 shows the output power and power-added efficiency for the 23.1 mm HFET. An 11.2 W output power was obtained with a PAE of 41% and a linear gain of 8.6 dB at 12 GHz. The power density is 480 mW/mm. An 8 W output power was obtained with a PAE of 48% and a linear gain of 9 dB at 12 GHz. This is the highest power and efficiency ever reported which is achieved by a single FET at this frequency.

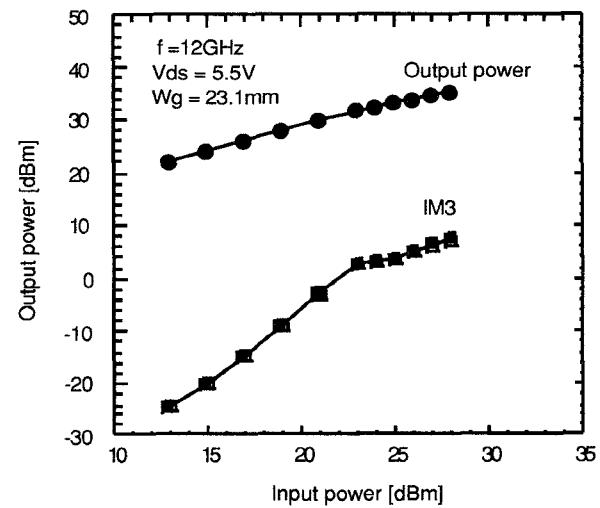

Figure 9 shows the third-order intermodulation distortion ( $IMD_3$ ) characteristics of the HFET. The frequency separation of the two tones is 5 MHz. The carrier-to-third-order intermodulation distortion ratio was as high as 29.0 dBc at 3 dB input backoff.

As shown in Fig.6, the  $I_{max}$  for an HFET is more than twice as much as the  $Id_{ss}$ , different from that of a MESFET. These results indicate that HFETs operate at a smaller  $Id_{ss}$  and a larger transconductance than MESFETs with the same output power. Thus, an HFET has an advantage over a MESFET for power applications.

## V. CONCLUSION

We developed an HFET with a high power and a high efficiency at Ku-band. 8 W and 11.2 W output powers were obtained with power-added efficiencies of 48% and 41% and linear gains of 9 dB and 8.6 dB at 12 GHz, respectively. This is the highest power and efficiency ever reported which is achieved by a single FET chip at this frequency.

Fig.9 IM3 and output power as a function of input power.

## REFERENCES

- [1] P.Saunier et al., "A HETEROSTRUCTURE FET WITH 75.8-PERCENT POWER ADDED EFFICIENCY AT 10 GHz," *1992 IEEE MTT-S International Microwave Symposium Digest*, vol. 2, pp. 635-638, June 1992.

- [2] S.T.Fu et al., "Ku-BAND HIGH POWER HIGH EFFICIENCY PSEUDOMORPHIC HEMT," *1994 IEEE MTT-S International Microwave Symposium Digest*, vol. 2, pp. 793-796, May 1994.

- [3] T.Simura et al., " 1 W Ku-band AlGaAs/GaAs Power HBTs with 72% peak power-added efficiency," *1994 IEEE MTT-S International Microwave Symposium Digest*, vol. 2, pp. 687-690, May 1994.

- [4] S.Takatani et al., "Thermal Stability of WSix/GaAs Interface", *J. Appl. Phys.*, 61, pp.220-224, 1987.

- [5] Y.Kohno et al. "K-band High Gain and High Reliability GaAs Power FET with Sub-half Micron WSi/Au T-shaped Gate", *IEEE GaAs IC Symposium Digest*, pp.137-140, 1994.